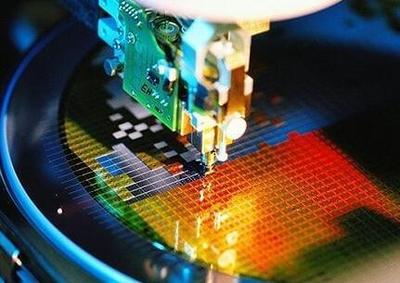

隨著半導(dǎo)體工藝不斷向更先進(jìn)節(jié)點(diǎn)邁進(jìn),超大規(guī)模集成電路的復(fù)雜度呈指數(shù)級(jí)增長(zhǎng),這使得芯片的可測(cè)試性成為設(shè)計(jì)流程中至關(guān)重要的一環(huán)。在2022年的行業(yè)培訓(xùn)與實(shí)踐中,可測(cè)性設(shè)計(jì)技術(shù)及其在集成電路芯片設(shè)計(jì)與服務(wù)領(lǐng)域的應(yīng)用,正以前所未有的深度和廣度被探討與實(shí)施。

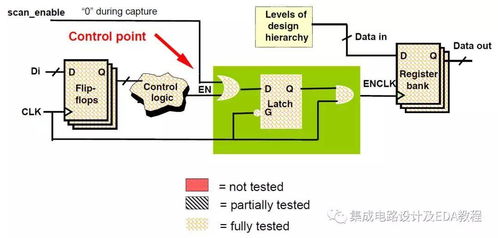

可測(cè)性設(shè)計(jì)是指在芯片設(shè)計(jì)階段就預(yù)先考慮并植入測(cè)試結(jié)構(gòu),以確保芯片制造后能夠被高效、低成本地測(cè)試,從而篩選出缺陷產(chǎn)品,保證出廠質(zhì)量和可靠性。對(duì)于包含數(shù)十億甚至上百億個(gè)晶體管的超大規(guī)模集成電路,傳統(tǒng)的測(cè)試方法已難以應(yīng)對(duì),DFT技術(shù)成為不可或缺的核心能力。

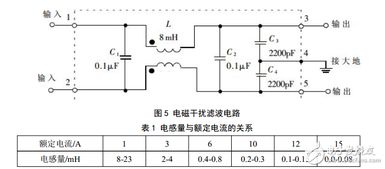

2022年的培訓(xùn)重點(diǎn)聚焦于幾大主流DFT技術(shù)及其最新發(fā)展。掃描鏈設(shè)計(jì)仍是基礎(chǔ),但更強(qiáng)調(diào)針對(duì)低功耗設(shè)計(jì)和時(shí)序收斂的優(yōu)化策略。內(nèi)建自測(cè)試技術(shù),特別是在存儲(chǔ)器測(cè)試和邏輯核測(cè)試方面,其算法與硬件實(shí)現(xiàn)結(jié)構(gòu)持續(xù)演進(jìn),以應(yīng)對(duì)更復(fù)雜的故障模型。邊界掃描技術(shù)不僅用于板級(jí)互聯(lián)測(cè)試,在芯片封裝和3D-IC堆疊測(cè)試中的作用也日益凸顯。基于壓縮的測(cè)試數(shù)據(jù)量縮減技術(shù)、測(cè)試功耗管理以及面向汽車電子等功能安全關(guān)鍵領(lǐng)域的DFT方法,都成為培訓(xùn)與實(shí)踐中的熱點(diǎn)。

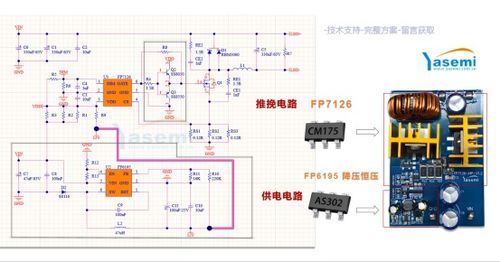

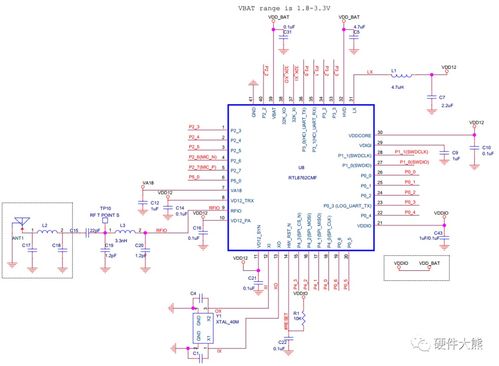

實(shí)踐層面,DFT已深度融入從RTL設(shè)計(jì)到物理實(shí)現(xiàn)的完整設(shè)計(jì)流程。領(lǐng)先的芯片設(shè)計(jì)公司與服務(wù)提供商正構(gòu)建高度自動(dòng)化的DFT插入、驗(yàn)證和模式生成流程。培訓(xùn)中強(qiáng)調(diào)“左移”理念,即在設(shè)計(jì)早期就進(jìn)行DFT規(guī)劃與集成,以避免后期因測(cè)試問(wèn)題導(dǎo)致的昂貴設(shè)計(jì)返工。云平臺(tái)和機(jī)器學(xué)習(xí)技術(shù)開始被應(yīng)用于DFT領(lǐng)域,例如利用AI優(yōu)化測(cè)試向量、預(yù)測(cè)測(cè)試覆蓋率以及進(jìn)行智能診斷,從而進(jìn)一步提升測(cè)試效率與質(zhì)量。

對(duì)于集成電路芯片設(shè)計(jì)及服務(wù)產(chǎn)業(yè)而言,強(qiáng)大的DFT能力已成為衡量其技術(shù)成熟度和服務(wù)競(jìng)爭(zhēng)力的關(guān)鍵指標(biāo)。專業(yè)的DFT團(tuán)隊(duì)不僅能為客戶設(shè)計(jì)出可測(cè)試性優(yōu)異的芯片,還能提供從DFT架構(gòu)咨詢、設(shè)計(jì)實(shí)現(xiàn)到測(cè)試程序開發(fā)、生產(chǎn)測(cè)試支持的全流程服務(wù)。在2022年,隨著芯片應(yīng)用場(chǎng)景拓展至人工智能、自動(dòng)駕駛、高性能計(jì)算等前沿領(lǐng)域,對(duì)DFT提出的挑戰(zhàn)也更為嚴(yán)峻,相應(yīng)的培訓(xùn)與實(shí)踐也更加注重跨學(xué)科知識(shí)的融合與解決實(shí)際工程問(wèn)題的能力培養(yǎng)。

總而言之,2022年圍繞超大規(guī)模集成電路可測(cè)性設(shè)計(jì)的培訓(xùn)與實(shí)踐,深刻反映了行業(yè)對(duì)芯片質(zhì)量與可靠性的極致追求。DFT技術(shù)已從一項(xiàng)輔助技術(shù)演變?yōu)轵?qū)動(dòng)芯片設(shè)計(jì)成功和制造盈利的核心支柱,持續(xù)推動(dòng)著集成電路芯片設(shè)計(jì)及服務(wù)行業(yè)向更高水平邁進(jìn)。